|

|

|

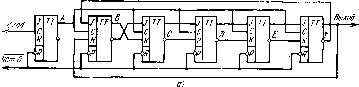

Главная -> Счетчики на транзисторах б ход г УстЛ дход Уст. О Рис. 13. Декады на основе сдвигающих регис1ров дыход  Вход Уст. О Z7 ГГ Рис. 14. Декады на сдвоенных трштерах 1 г 3 5 ff 7 8 S rj дход Выход Рис. 15. Временная диаграмма Рис. 16. Схема делителя на 6 на JK-тригге-работы декад на рис. 14 pax феменные диаграммы работы этих декад аналогичны декаде по схеме рис. 4. При использовании сдвоенных JK- или D-триггеров целесообразно построе-ine декад по схемам рис. 14,а и б соответственно. Принцип работы таких де-сад проиллюстрирован на рис. 15. Первый триггер делит частоту входного сигнала на 2. Пять остальных триггеров соединены в кольцевой сдвигающий регистр. При установке декады в О на выходе В сдвигающего регистра уста-1авливается низкий уровень, на остальных выходах (кроме Л) - высокий. При 14 подаче каждого второго импульса низкий уровень появляется поочередно на остальных четырех выходах регистра С, D, Е, F. Временная диаграмма декады на рис. 14,6 отличается от рассмотренной лишь полярностью входных импульсов. В декадах на основе сдвигающих регистров (см. рис. 13,а и 14,а) можно применять как синхронные, так и универсальные триггеры. В радиолюбительской практике делители частоты на 6 занимают важное место. Их применяют в счетчиках десятков секунд и минут электронных часов. Делители на 6 строят так же, как и декады, но число триггеров в них соответственно меньше. Схема наиболее простого делителя на 6, выполнимого как на синхронных, так и на универсальных JK-триггерах, приведена на рис. 16, а его временная диаграмма - на рис. 17. Первый триггер делит входную частоту на 2, два следующих - на три. Нетрудно видеть, что этот делитель напоминает декады, приведенные на рис. 8, из которых исключен один триггер. Аналогично могут быть модифицированы и другие декады. На рис. 18 показана схема делителя на 6 на трех D-триггерах, его временная диаграмма приведена на рис. 19. Схемы делителей на 6 на основе сдвигающих регистров приведены на рис. 20. Рис. 20,а и б - схемы на трех JK- и D-триггерах, соединенных в сдвигающий регистр с перекрестной связью. Делители по схемам рис. 20,в и г представляют собой включенные последовательно делители на 2 и на 3 соответственно на JK- и D-триггерах. Временные диаграммы делителей по схемам рис. 20 подобны диаграммам соответствующих декад. / 2 J 4 S S Г-LJ-l. J-L вход дыход Рис. 17. Временная диаг- Рис. 18. Схема делителя на 6 на D-триггерах рамма работы делителя на 6 рис. 16 / г 3 5 6 Bxods\r\i\rvrvr Рис. 19. Временная диаграмма работы де- лителя на 6 рис. 18 q Необходимый в часах счетчик с коэффициентом пересчета 24 обычно строится как декада, два триггера и элемент совпадения, сбрасывающий показания счетчика на нуль при достижении им состояния 24. На рис. 21, где приведена схема такого счетчика, декада, работающая в коде 1-2-4-8, помечена знаком СТ10. Пока число поступивших на вход импульсов не превышает 23, счетчик считает как обычно: декада считает единицы часов, два триггера - десятки. После поступления 20-го импульса с выхода Q интегральной микросхемы ИШСч уровень логической 1 поступает на первый вход элемента И-НЕ ИШСъ, а после 24-го уровень логической 1 с выхода 4 декады поступает на второй вход MMC3Si, в результате чего включается элемент ИМСз& и низкий уровень сигнала с его выхода, пройдя через элементы ИМСзб и ИМСъв, поступает на входы R декады и триггеров и сбрасывает показания счетчика. При использовании декад, работающих в невесовых кодах, второй вход элемента ИМСъл следует подключать к выходу С (см. рис. 9, 11), D (см. рис. 13) или D (см. рис. 14). Среди рассмотренных выше декад и делителей нетрудно найти кроме д# лнтелей на 2, 4, 6, 8, 10 счетчики с коэффициентом пересчета 3 и 5, Если не-вбходимый коэффициент пересчета раскладывается на приведенные выше со-множители, счетчик собирают нз нескольких последовательно включенныж де лятелей, например счетчик с коэффициентом пересчета 9 составляют из дву делителей на 3. дход Уст. О . Вход Уст. О Вход Уст, О г-ЯУ Выход Выход Выход Jxod i -S- о У от. У Выход Рис. 20. Схемы делителя на 6 на основе сдвигающих ре гистров Зход Уст. о HMBf ИМСг

\ ИМ С за ffMd35 dss Рис, 21. Счетчнк с коэффициентом пересчета 24

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||