|

|

|

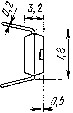

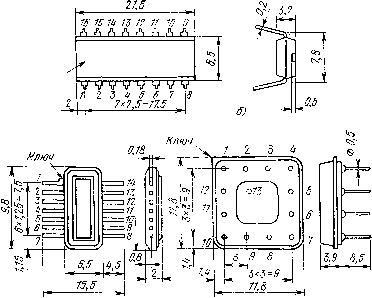

Главная -> Счетчики на транзисторах ство представляет собой пятиразрядный сдвигающий регистр, собранный на транзисторах Тх-Тю. Каждый разряд регистра - это триггер, в котором резисторы Ri и R2 (см. рис. 1), управляющие работой диодно-емкостных ключей, отсоединены от коллекторов транзисторов данного разряда и подключе- 7 2 и 5 е 7 8 д в с . Рис. 5. Временная диаграмма работы декады на основе сдвигающего регистра ы к выходам триггеров предыдущего разряда. Выход последнего, пятого, разряда регистра подключен ко входу первого, причем полярность сигналов обратной связи изменена на противоположную. Временная диаграмма работы декады приведена на рис. 5. Верхняя диаграмма изображает Ихмпульсы на входе декады. Графики, помеченные буквами Л, В, С, D, Е, соответствуют напрялсениям на соответствующих выходах триггеров сдвигающего регистра. Для установки декады в О цепь питания коллекторов левых по схеме плеч триггеров разрывается, при этом на выходах Л, В, С, Д Е устанавливается низкий уровень напряжения. Через резисторы R29 и R30 (см. рис. 4) уровни с выхода пятого триггера (транзисторы Ti и Гг) поступают на диодно-емкостные ключи С9Д9 и СДю, Диод Дэ приоткрывается, диод Дю закрыт. При поступлении первого счетного импульса отрицательной полярности (или спада импульса положительной полярности) транзистор Гд закрывается током, текущим через диод Дэ и конденсатор Cg. Триггер на транзисторах Гд, Тю переключается в единичное состояние, на выходе А появляется высокий уровень. На остальных выходах триггеров сохраняется низкий уровень напряжения. При поступлении последующих счетных импульсов, вплоть до пятого, триггеры поочередно устанавливаются в состояние 1, импульсы с шестого по десятый поочередно устанавливают триггеры регистра в состояние 0. К выходу Е декады можно подключать вход следующей декады. Описанными выше двумя схемами декад, конечно, не исчерпывается многообразие возможных схем, однако приведенные схемы в некоторых отношениях оптимальны. Декада по первой схеме содержит практически минимально возможное число деталей, вторая обладает быстродействием, равным быстродействию отдельного триггера, и также достаточно проста. СЧЕТЧИКИ НА ИНТЕГРАЛЬНЫХ МИКРОСХЕМАХ МАЛОЙ СТЕПЕНИ ИНТЕГРАЦИИ Количество элементов в счетчиках можно значительно уменьшить, если применить интегральные микросхемы. Отечественная промышленность выпускает большое количество различных типов интегральных микросхем, в том числе триггеров и счетчиков. Здесь будут рассмотрены счетчики на микросхемах, содержащих в корпусе один-два счетных триггера. Триггеры микросхем достаточно сложны. Они содержат, как правило, десятки транзисторов и резисторов, однако практически все они по принципу действия могут быть разбиты на две большие группы -JK- и D-триггеры. Параметры и разводка выводов некоторых интегральных микросхем, содержащих JK- и D-триггеры, приведены в табл. 1, а чертежи их корпусов - на рис. 6. Интегральные микросхемы серий К155, К131, К158 выпускаются в пластмассовых корпусах с 14 выводами (рис. 6,а), часть серии К155 с 16 выводами (рис. 6,6), интегральные микросхемы серий К130, К133, К134, К136 -в металлостеклянных корпусах с планарными выводами (рис. 6,в), серии Kl? - в корпусах со штыревыми выводами (рис. 6,г). Таблица !

Примечания: 1. Интегральные микросхемы К217ТК1А, К217ТК1Б требуют напряжения питания 6 В± 10% и 3 В± 10%. остальные 5 В ±5%. 2. В скобках указаны номера выводов второго триггера. r-oi7TTriA voij-rviT итилл .! / и ? глрлурт гпрпинить 3. Для нормального функционирования триггеров интегральных микросхем К217ТК1А и К217ТК1Б выводы 1 и 3 следует соединить. Рассмотрим вначале работу JK-триггера. Триггер этого типа имеет обычно не менее пяти входов: i/? - вход установки в О, S - вход установки в 1, С - вход тактовых импульсов, J и К - управляющие входы, Q и Q - прямой и инверсный выходы. При поступлении низкого уровня на вход R триггер устанавливается в нулевое состояние О, на вход S - в состояние 1. Зона илюча 7 73 11 7f 70 д 8 Л Л Л Л Л Л Л У У У У У У 1\ 1 Ъ 5 6 Sl,5-75  Зона нпюча  В) 8) Рис. 6. Чертежи корпусов микросхем различных серий Сложнее работа триггера при подаче сигналов на входы С, J и К. Здесь следует различать триггеры двух разновидностей - универсальные и синхронные. Наиболее простой режим работы универсального JK-триггера осуществляется при высоком уровне напряжения на входах J и К. В этом случае JK-триггер работает как обычный триггер со счетным входом: при поступлении каждого импульса на тактовый вход С (точнее, после спада импульса) состояние триггера меняется на противоположное. Если на входах J и К установлен низкий уровень, то состояние триггера при подаче импульсов на вход С не меняется. Если на входе / высокий уровень, а на входе К низкий, то после спада импульса на входе С на выходе Q появляется высокий уровень, а на выходе Q низкий, и наоборот, если на входе / низкий уровень, на входе К высокий, то на выходе Q появляется низкий уровень, на выходе Q -

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||