|

|

|

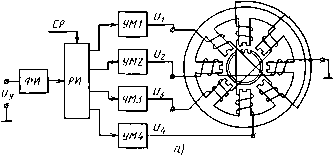

Главная -> Разомкнутые системы радиоавтоматики средством понижающего редуктора. Частота приемистости, характеризующая наибольшую частоту следования управляющих импульсов, отрабатываемую двигателем без сбоев, достигает 4-6 кГц. Различают шаговые двигатели с механической и электромагнитной связью между ротором и статором. Примером первого типа двигателей является шаговый искатель с храповым колесом, ранее широко применявшийся в автоматических телефонных станциях. Их недостаток - низкая частота приемистости и малый ресурс работы.  1 2 5 и 5 6 7 в 9 10 П 12 13 П Нппппппппппппп иг\ 1 Рис, 7.21 В системах управления наибольшее распространение получили шаговые двигатели с электромагнитной связью ротора и статора. В пазах статора такого двигателя уложено несколько обмоток управления, оси которых имеют взаимное смещение по углу. Ротор представляет собой либо постоянный магнит, либо сердечник с обмоткой возбуждения. Для осуществления вращения ротора в одном направлении статорные обмотки поочередно подключаются к источнику управляющего напряжения, что приводит к повороту магнитного поля в статоре. Изменение направления вращения достигается изменением очередности включения обмоток. Необходимые коммутации токов в обмотках выполняются специальной схемой управления двигателем. Число статорных. обмоток управления в шаговых двигателях различных типов может составлять I, 2, 3, 4 или более. Реверсирование возможно при наличии более двух обмоток. Увеличение числа обмоток управления приводит к возрастанию частоты приемистости и КПД двигателя, но заставляет усложнять схему управления. Наиболее распространены трех- и четырехобмоточные шаговые двигатели. Ротор и статор имеют большое число зубцов (полюсных выступов), выполненных так, что с зубцами ротора одновременно может полностью совпадать лишь часть зубцов статора. Этим достигается уменьшение шага до величины Аф=3607(шоШз), где Шс- число пространственно сдвинутых обмоток управления; 1щ - число зубцов на роторе. Упрощенная схема включения обмоток четырехобмолочного шагового двигателя показана на рис. 7.21, а, где Uy- управляющие импульсы; Ui (( = 1,2,3,4) - импульсы напряжения на обмотках статора; ФИ - формировать импульсов; РИ - распределитель импульсов; УМ;- усилитель мощности. Формирователь импульсов преобразует входные импульсы произвольной формы в прямоугольные импульсы требуемой длительности. Распределитель импульсов преобразует единичный код в четырехфазную систему прямоугольных импульсов напряжения, которая через усилители мощности подается наста-торные обмотки. Соответствующие временные диаграммы представлены на рис. 7.21, б. При необходимости изменения направления вращения на распределитель импульсов подается сигнал реверсирования CP, изменяющий последовательность подачи импульсов в статорные обмотки. Усилители мощности для шаговых двигателей малой мощности (десятки ватт) строят иа транзисторах, а для силовых двигателей - на тиристорах. Цифровые управляюшие фильтры. Алгоритм работы линейного цифрового фильтра описывается рекуррентной формулой Xi [п] =2 &,-л;[п -/]- 2 /1 h -/] (7-87) 1=0 /=1 где X [п] и xjn] - числа на входе и выходе фильтра. В случае, когда все коэффициенты aj нулевые, фильтр называют нерекурсивным, в общем случае - рекурсивным. Формула (7.87) взаимно однозначно связана с дискретной передаточной функцией фильтра D{z). Нерекурсивному фильтру соответствует дискретная передаточная функция, знаменатель которой тождественно равен единице. Алгоритм (7.87) можно реализовать либо схемными, либо программными средствами. При схемной реализации строят узкоспециализированный вычислитель, содержащий соединенные в единой непере-страиваемой схеме элементы памяти, перемножители и сумматоры в количестве, зависящем от числа соответствующих операций в алгоритме (7.87). Программную реализацию производят на базе управляющей ЦВМ или микропроцессора, выполняющих вычисления по заданной программе. В обоих случаях при разработке цифрового фильтра должны быть Оценены требования к быстродействию, количеству ячеек памяти и ширине разрядной сетки вычислителя или ЦВМ. Они зависят не только от вида алгоритма (7.87) и свойств замкнутой системы в целом, но также от выбранной формы построения вычислительного алгоритма. Используются в основном четыре таких формы [2, 19, 13]. Прямая форма (рис. 7.22) требует l+in элементов задержки. Каноническая форма (рис. 7.23) позволяет уменьшить требуемое число элементов задержки до значения, равного максимальному из чисел / и т. Это объясняется отсутствием разделения на элементы за- Ьо Ь, 0-*е- Рис. 7.22 держки для входных и выходных величин - на одном и том же элементе производится задержка и тех и других. Последовательная (каскадная) форма (рис. 7.24) предполагает представление дискретной передаточной функции D (г) в виде произ- хт Г Рас. 7.23 ведения L более простых дискретных передаточных функций обычно первого или второго порядка. Параллельная форма (рис. 7.25) является следствием представления функции D (г) в виде суммы М более простых дискретных передаточных функций. Каждое из получающихся элементарных цифровых звеньев реализуется с использованием либо прямой, либо канонической формы. [л] в, и) 4> Пм(г} Рис. 7.24 Рис. 7.25 Требуемое быстродействие вычислителя легко оценить исходя из необходимости выполнения всех арифметических операций, связанных с получением очередного выходного числа [п], в пределах одного периода дискретности Т (или определенной части периода ди-

|